# Architecture des ordinateurs

# par Christophe TOMBELLE

Télécom LILLE

Tous droits de traduction, de reproduction et d'adaptation réservés pour tous pays.

© ENIC, Telecom Lille1, Telecom Lille, 2000

La loi du 11 mars 1957 n'autorisant, aux termes des alinéas 2 et 3 de l'article 41, d'une part, que les "copies ou reproductions strictement réservées à l'usage du copiste et non destinées à une utilisation collective" et d'autre part, que les analyses et que les courtes citations dans un but d'exemple et d'illustration, "toute représentation intégrale ou partielle, faite sans le consentement de l'auteur ou de ses ayants droits, ou ayants cause est illicite" (alinéa 1<sup>er</sup> de l'article 40).

Cette représentation ou reproduction, par quelque procédé que ce soit, constituerait donc une contrefaçon sanctionnée par les articles 425 et suivants du code pénal.

Télécom Lille - Cité Scientifique Rue G. Marconi – BP20145 59653 Villeneuve d'Ascq Cedex Tél.: 03.20.33.55.77 http://www.telecom-lille1.eu

# Table des matières

| 1. Le matériel                                           | 7  |

|----------------------------------------------------------|----|

| 1.1. Système à microprocesseur                           | 7  |

| 1.2. Les bus                                             | 8  |

| 1.3. Constitution interne du microprocesseur             | 13 |

| 1.4. Constitution interne de la mémoire                  | 14 |

| 1.5. Entrées - sorties                                   | 15 |

| 1.6. Fonction décodage                                   | 18 |

| 1.7. Actions du microprocesseur                          | 18 |

| 1.8. Le port série                                       | 18 |

| 1.9. Constitution                                        | 19 |

| 1.10. Brochage                                           | 20 |

| 1.11. Microcontrôleur                                    | 20 |

| 2. Le matériel : travail dirigé                          | 23 |

| 2.1. Déroulement d'une séquence d'instructions           | 23 |

| 2.2. Chronogramme de lecture                             | 24 |

| 2.3. Performances des processeurs                        | 24 |

| 3. Le logiciel : modèle de programmation                 | 27 |

| 3.1. Organisation de la mémoire                          | 27 |

| 3.2. Le modèle de programmation                          | 28 |

| 3.3. Segmentation du 8086                                | 30 |

| 3.4. Représentation à la Turbo-Debugger                  | 32 |

| 3.5. Association par défaut des registres de segment     | 34 |

| 3.6. Méthodologie                                        | 35 |

| 4. Représentation des données                            | 37 |

| 4.1. Les modes d'adressage                               | 37 |

| 4.2. L'adressage immédiat                                | 37 |

| 4.3. L'adressage direct                                  | 37 |

| 4.4. L'adressage indirect                                | 38 |

| 4.5. L'accès aux variables                               | 42 |

| 4.6. Plate-forme Turbo-C 8086 (taille des types de base) | 45 |

| 4.7. Schémas de mémoire                                  | 45 |

| 4.8. Sujet du TP2                                        | 46 |

| 5. Structuration des données                   |    |

|------------------------------------------------|----|

| 5.1. Les pointeurs                             | 47 |

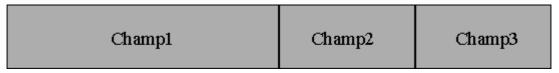

| 5.2. Les enregistrements                       | 49 |

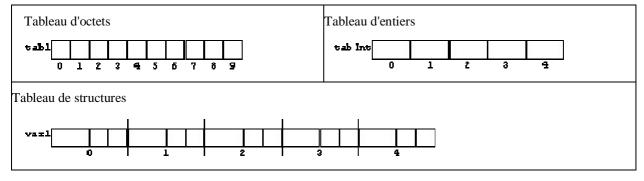

| 5.3. Tableau d'octets                          | 50 |

| 5.4. Tableaux d'entiers                        | 50 |

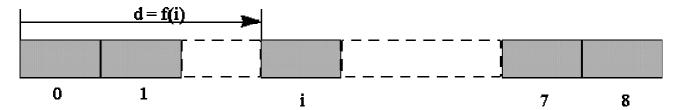

| 5.5. Tableau d'enregistrements                 | 50 |

| 5.6. Tableaux à 2 dimensions                   | 51 |

| 5.7. Tableau de pointeurs                      | 51 |

| 5.8. Fin du TP2                                | 52 |

| 6. Structuration du code                       | 53 |

| 6.1. Les instructions de saut                  | 53 |

| 6.2. Les structures de contrôle                | 55 |

| 6.3. Sujet du TP3                              | 57 |

| 7. Structuration du code : les sous-programmes | 61 |

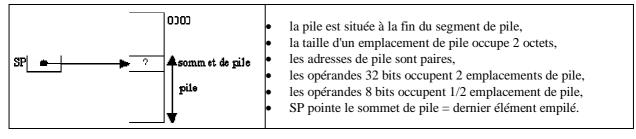

| 7.1. Fonctionnement d'une pile                 | 61 |

| 7.2. Représentation de la pile                 | 61 |

| 7.3. L'appel de sous-programme                 | 61 |

| 7.4. Retour de sous-programme                  | 62 |

| 7.5. Imbrication des sous-programmes           | 63 |

| 7.6. Fonctions                                 | 63 |

| 8. Passage des arguments                       | 65 |

| 8.1. Le passage des arguments en langage C     | 65 |

| 8.2. Passage des arguments par la pile         | 65 |

| 8.3. Point de vue de l'appelant                | 66 |

| 8.4. Point de vue de l'appelé                  | 66 |

| 8.5. Exploitation du résultat de la fonction   | 67 |

| 8.6. Récursivité                               | 68 |

| 8.7. Paramètres en nombre variable             | 68 |

| 9. Gestion des entrées-sorties                 | 69 |

| 9.1. Introduction                              | 69 |

| 9.2. Le polling                                | 69 |

| 9.3. Le mécanisme d'interruption               | 69 |

| 9.4. Le contrôleur d'interruptions             | 70 |

| 9.5. Vectorisation des interruptions           | 70 |

| 9.6. Les interruptions logicielles             | 71 |

| 9.7. Mécanisme d'accès direct à la mémoire     | 71 |

| 10. Les logiciels d'exploitation                      |    |

|-------------------------------------------------------|----|

| 10.1. Rôle d'un système d'exploitation                | 73 |

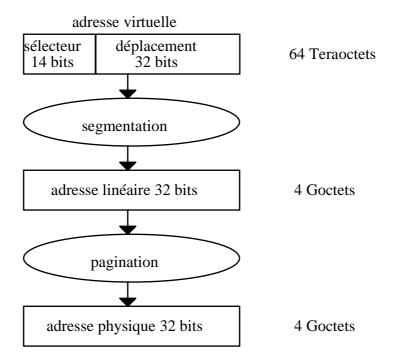

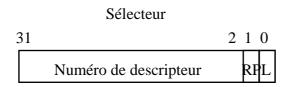

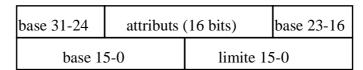

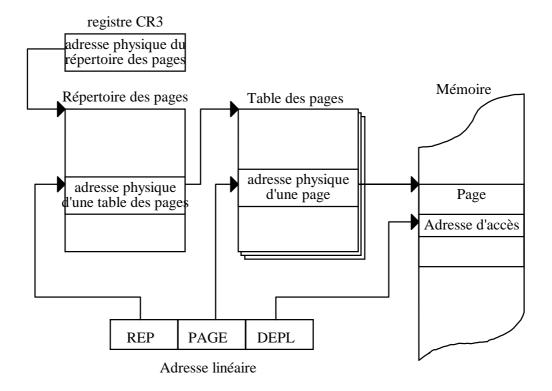

| 10.2. La gestion de la mémoire                        | 74 |

| 10.3. Le parallélisme d'exécution                     | 81 |

| 10.4. La notion de protection                         | 83 |

| 11. Système d'exploitation : approfondissement        | 87 |

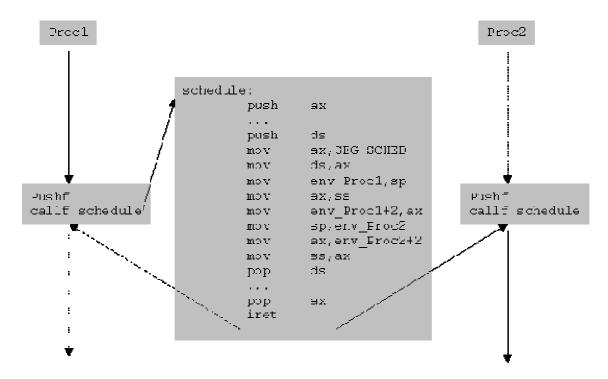

| 11.1. Implantation du pseudo-parallélisme             | 87 |

| 12. Evolution des performances                        | 91 |

| 12.1. Introduction                                    | 91 |

| 12.2. Structure d'un ordinateur                       | 91 |

| 12.3. Progrès technologiques                          | 91 |

| 12.4. Amélioration des performances                   | 91 |

| 12.5. L'architecture RISC                             | 93 |

| 12.6. Architectures, super-pipeline et super-scalaire | 94 |

| 12.7. Processeurs CISC                                | 94 |

| 12.8. L'architecture VLIW                             | 95 |

| 12.9. Applications                                    | 95 |

| 13 Rihliographie                                      | 97 |

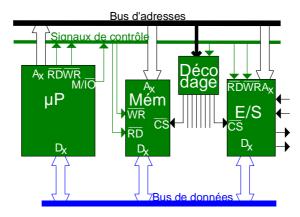

# 1.1. Système à microprocesseur

Le microprocesseur est capable d'exécuter des instructions qui agissent sur des opérandes. Les opérandes sont constitués d'une part des **registres** situés au cœur du processeur et d'autre part des variables situés dans la **mémoire**. Les **instructions** que le microprocesseur doit exécuter sont des *informations codées* qui résident également *en mémoire*. Le codage employé pour les instructions est propre au modèle de microprocesseur employé. Ce codage obéit à une certaine logique, logique que le microprocesseur emploie pour le décodage. L'ensemble des instructions qu'un microprocesseur est capable d'exécuter forme son **jeu d'instructions**.

Le processeur désigne les cases mémoires auxquelles il veut accéder en présentant leurs adresses sur le **bus d'adresses**. L'ensemble des signaux d'adresses d'un système s'appelle un **bus d'adresses**. Le nombre de signaux d'adresses détermine la **capacité d'adressage**. Avec 1 signal d'adresse supplémentaire, on peut désigner 2 fois plus de cases mémoire. Autrement dit, on double la capacité d'adressage. Ainsi, avec 1 seul signal d'adresses un processeur serait capable d'adresser 2 octets, avec 2 signaux d'adresses, il pourrait en adresser 4. Avec 16 signaux, le 8085 peut en adresser 2<sup>16</sup> soit 64 ko, avec 20 signaux d'adresses, le 8086 peut en adresser 2<sup>20</sup> soit 1 Mo, avec ses 32 signaux le 386 peut en adresser 2<sup>32</sup>, soit 4 Go.

La mémoire échange des informations avec le processeur par le **bus de données** qui est bidirectionnel. Le processeur précise également l'instant et le sens du transfert grâce aux **signaux de contrôle** que sont les signaux de lecture et d'écriture.

Il existe de la mémoire accessible en lecture et en écriture (**RAM=Random Access Memory ou mémoire vive**) et de la mémoire accessible uniquement en lecture (**ROM=Read Only Memory ou mémoire morte**).

Le processeur comporte des registres non seulement pour les opérandes des opérations qu'il exécute mais aussi pour des usages plus techniques. Par exemple, l'adresse de la prochaine instruction à exécuter est contenue dans un registre du microprocesseur : le **pointeur d'instructions** (IP = Instruction Pointer), plus généralement appelé **compteur de programme** (PC = Program Counter). Le microprocesseur commence chacun de ses cycles de fonctionnement par un cycle de lecture en mémoire. Il va ainsi chercher le code de l'instruction à exécuter. Ce code transite sur le bus de données jusqu'au microprocesseur.

Celui-ci décode l'instruction et décide de la suite à donner à l'instruction. Eventuellement, des compléments d'instructions sont nécessaires pour que l'instruction soit complète. En effet, une **instruction** nécessite généralement un ou plusieurs opérandes; elle peut donc faire l'objet de **plusieurs cycles** de lecture en mémoire pour être complète.

La lecture des codes machine relève d'un comportement spontané du microprocesseur (que dois-je faire ?) l'exécution des codes machines définit le comportement programmé du microprocesseur : faire ceci, faire cela. Le fonctionnement d'un microprocesseur alterne entre comportement spontané et comportement programmé. Spontanément, le microprocesseur acquiert un code machine sous forme d'un ou plusieurs mots mémoire. Lorsque l'instruction est complète, il l'exécute. Cette exécution peut comporter une lecture ou une écriture en mémoire. Ensuite, le processeur

recommence avec l'instruction suivante. Dès qu'un processeur est sous tension, il acquiert spontanément des codes machine et les exécute. Les premiers codes machine proviennent d'une ROM car à la mise sous tension, le contenu d'une RAM est indéterminé tandis que celui d'une ROM, déterminé par le constructeur de l'ordinateur est maintenu en l'absence d'énergie.

### 1.2. Les bus

Les architectures à microprocesseur font appel à des voies de circulation des informations appelées bus. Un bus relie plusieurs dispositifs ensemble. Un câblage en bus est plus économique et plus évolutif qu'un câblage en réseau complètement maillé. Sur un bus, les informations ne proviennent pas toujours du même émetteur et n'ont pas toujours le même destinataire. Ainsi, une broche d'un dispositif peut :

- soit émettre un signal,

- soit ne pas émettre de signal mais au contraire écouter un signal émis par un autre dispositif,

- soit ne pas émettre de signal et ignorer un éventuel signal émis par un autre dispositif

La logique à 3 états autorise ce type de connexion.

### 1.2.1. Logique à 3 états

### 1.2.1.1. Le problème

En logique classique à 2 états, les règles de conception interdisent de connecter deux sorties ensemble : un signal ne peut être émis que par une source unique, il ne peut en aucun cas venir "soit d'une porte, soit d'une autre".

#### 1.2.1.2. Structure interne

8

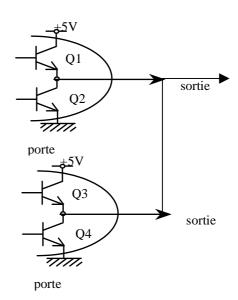

Dans une porte classique à 2 états, l'un au moins des deux transistors de l'étage de sortie est passant. Si on relie deux sorties ensemble et que ces sorties cherchent à imposer des états logiques différents sur leur sortie respective, un transistor de l'un et un transistor de l'autre étant passants (Q1 et Q4 passants ou Q3 et Q2 passants), un court-circuit est établi entre l'alimentation et la masse, générant un courant destructeur pour les deux portes. En pratique, une résistance en série avec le collecteur de Q1 ou Q3 limite le courant de sortie de la porte pour éviter cette destruction. Il reste que la tension résultante à la sortie de cette porte ne correspond ni à un 1 ni à un 0.

En plus des 2 états logiques habituels, la logique à 3 états fait intervenir un troisième état, technologique celui-là, qui correspond à l'état haute impédance. Dans l'état haute impédance, les deux transistors de sortie sont bloqués. Les états logiques 0 et 1 correspondant à un transistor passant, ce sont des états "basse impédance".

| Q1     | Q2     | Etat             | ~5V              |

|--------|--------|------------------|------------------|

| bloqué | Bloqué | Hi-Z             | Q1               |

| bloqué | Saturé | 0                | sortie           |

| saturé | Bloqué | 1                | \\\ \tag{\alpha} |

| saturé | Saturé | Auto destruction | 77777<br>porte   |

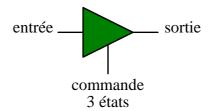

#### 1.2.1.3. Porte à 3 états

Une porte à 3 états est capable de générer sur sa sortie les 3 états de la logique à 3 états : 0, 1 ou Z (haute impédance)

Ceci est une porte non inverseuse, c'est-à-dire un simple répéteur, mais comportant en plus une entrée de commande du 3ème état. Le fonctionnement est le suivant : soit la porte est active et la sortie recopie l'état de l'entrée, soit la porte est inactive et la sortie est en haute impédance.

### 1.2.1.4. Schéma équivalent

Quand la sortie est en haute impédance, tout se passe comme si la sortie de la porte était coupée (interrupteur ouvert)

Une entrée "en l'air" est une entrée non pilotée par une sortie. Une entrée en l'air est dans l'état haute impédance. En effet, il n'y a pas de différence entre une entrée en l'air et une entrée reliée à une sortie dans l'état haute impédance (interrupteur ouvert).

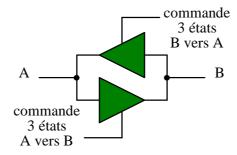

### 1.2.1.5. Porte bidirectionnelle

Si on met deux portes 3 états en "parallèle-inverse", on réalise une barrière bidirectionnelle 3 états. Le processeur et les mémoires sont des composants capables de gérer la logique 3 états, c'est-à-dire qu'ils comportent des broches bidirectionnelles de ce type autorisant les fonctionnements suivants :

- fonctionnement A vers B (entrée côté A, sortie côté B, porte du bas en haute impédance)

- fonctionnement B vers A (entrée côté B, sortie côté A, porte du haut en haute impédance)

- fonctionnement A isolé de B (les deux portes en haute impédance)

Les côtés A et B sont bidirectionnels 3 états. Du côté A, on peut :

- soit émettre un signal,

- soit ne pas émettre mais recevoir un signal,

- soit ne pas émettre ni recevoir un signal.

A et B étant identiques, ce qui a été dit pour le côté A est vrai pour le côté B.

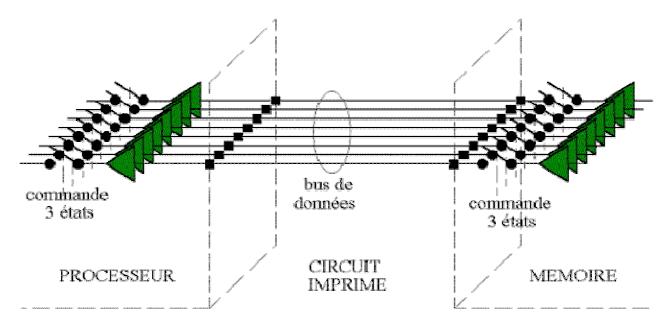

### 1.2.2. Bus de données et d'adresses

Un bus de données est un ensemble de signaux reliant des dispositifs à broches bidirectionnelles à 3 états. Le bus d'adresses relie les sorties à 3 états du bus d'adresses du processeur avec les entrées du bus d'adresses des autres dispositifs, mémoire, contrôleurs d'entrée-sortie, logique de décodage.

#### 1.2.2.1. Cas de la lecture

En lecture, les informations circulant sur le bus de données vont de la mémoire vers le processeur. Le dispositif "**parleur**" (interrupteurs fermés sur les sorties) est la mémoire, le dispositif "**écouteur**" (interrupteurs fermés sur les entrées) est le processeur.

En l'absence d'échanges d'information entre la mémoire et le processeur, le bus de données est en haute impédance. Aucun dispositif ne présente d'état sur le bus de données. En revanche, lorsqu'un échange a lieu, le bus de données est en basse impédance. Il présente l'impédance de la sortie du composant qui "parle" sur le bus de données.

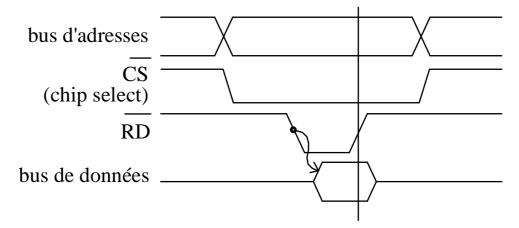

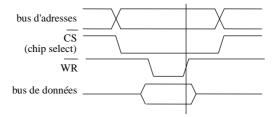

### 1.2.2.2. Cycle de lecture

Mémoire est validée => données apparaissent; sur le front montant de RD# le processeur prend en compte les données

Un cycle de lecture est un transfert de données de la mémoire vers le processeur. Une lecture se produit spontanément lorsque le processeur a besoin de lire un code machine. Une lecture peut également résulter de l'exécution d'une instruction qui a besoin de la valeur d'une variable. Une lecture résulte d'un comportement spontané ou programmé du processeur.

L'adresse véhiculée sur le bus d'adresses provient du processeur. La donnée véhiculée sur le bus de données provient du bus de données. Le signal RD# est contrôlé par le processeur. Le signal de chip select (sélection de boîtier) est élaboré à partir des signaux d'adresses. Le signal RD# correspond sur la mémoire à une broche de même nom ou parfois appelée OE# (Output Enable). On peut retenir du signal RD# qu'il est une impulsion de lecture dont l'action reste conditionnée bien sûr par la sélection du boîtier.

Au départ, le bus de données est en haute impédance.

- le microprocesseur présente les adresses

- donc le CS# (chip select) de la mémoire concernée s'active

- le microprocesseur active le signal RD#

- la mémoire présente sur le bus de données le contenu de la case mémoire adressée

- le microprocesseur prend en compte les données présentes sur le bus de données

- le microprocesseur désactive le signal RD#

- la mémoire relâche le bus de données en haute impédance.

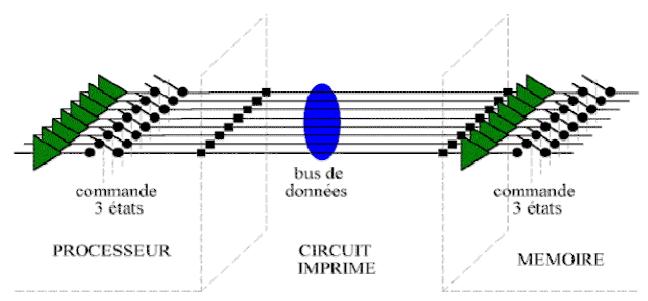

### 1.2.2.3. Cas de l'écriture

En écriture, les informations circulant sur le bus de données vont du processeur vers la mémoire. Le dispositif "**parleur**" (interrupteurs fermés sur les sorties) est le processeur, le dispositif "**écouteur**" (interrupteurs fermés sur les entrées) est la mémoire.

### 1.2.2.4. Cycle d'écriture

Un cycle d'écriture est un transfert de données du processeur vers la mémoire. Une lecture résulte de l'exécution d'une instruction de mise à jour d'une variable, donc d'un comportement programmé du processeur.

L'adresse véhiculée sur le bus d'adresses et la donnée véhiculée sur le bus de données proviennent du processeur. Le signal WR# est contrôlé par le processeur.

- le microprocesseur présente les adresses sur le bus d'adresses

- donc le chip select de la mémoire concernée s'active

- le microprocesseur présente sur le bus de données la donnée à écrire dans la case adressée

- le microprocesseur active le signal WR#

- le microprocesseur désactive le signal WR#

- le microprocesseur relâche le bus de données en haute impédance

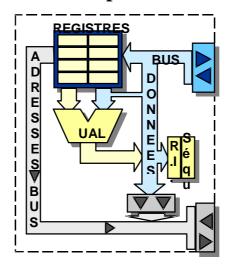

# 1.3. Constitution interne du microprocesseur

Un microprocesseur fonctionne avec une horloge. Parfois l'oscillateur est interne, parfois externe. Le quartz est connecté aux bornes de l'oscillateur.

L'ALU sait effectuer des opérations arithmétiques (4 opérations) ou logiques (et, ou, non, ou exclusif, décalages et rotations) sur des entiers. Les opérations s'effectuent sur 1 ou 2 opérandes.

Les opérandes proviennent des registres du microprocesseur ou de la mémoire (externe) via le bus de données.

Il y a éventuellement un additionneur dédié à des calculs d'adresses.

Le registre instruction R.I. stocke le code machine de l'instruction à exécuter. Le séquenceur organise l'exécution des instructions. Par exemple, une instruction d'addition pourra spécifier qu'un des opérandes vient de telle case mémoire que l'autre vient de tel registre du microprocesseur. L'adresse de la case mémoire fait partie du code machine. Le séquenceur s'arrangera pour ouvrir le buffer bidirectionnel du bus de données en lecture, pendant qu'il génèrera un 0 sur le signal RD#. L'opération d'addition sera sélectionnée sur l'ALU et tel registre sera sélectionné parmi le jeu de registres du microprocesseur.

Les séquenceurs peuvent être câblés ou microprogrammés. De l'optimisation d'un microprogramme, dépend l'efficacité du processeur. Un microprogramme est constitué d'une succession de mots dont chaque bit commande un dispositif interne du processeur.

Les microprocesseurs les plus simples ne savent pas effectuer de multiplication ou de division en une seule instruction. Ils ont alors recours à un programme de multiplication ou de division. Les calculs effectués sur des nombres à virgule peuvent également faire l'objet de sous-programmes. Une autre solution consiste à recourir à un coprocesseur. C'est un processeur spécialisé dans les calculs des nombres à virgule.

Les processeurs puissants intègrent le "coprocesseur" sur leur puce. On ne parle plus de coprocesseur mais d'unité de calculs en virgule flottante. L'architecture matérielle des processeurs et des systèmes à hautes performances sera étudiée plus tard.

La logique d'interruption, non représentée sur ce schéma, sera étudiée ultérieurement avec les autres techniques de gestion des entrées-sorties.

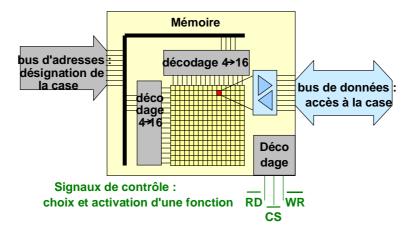

### 1.4. Constitution interne de la mémoire

En dehors de ses registres, un microprocesseur ne contient pas de mémoire<sup>1</sup>. Un microprocesseur, notamment ne contient pas le programme qu'il exécute. La mémoire est donc un composant indispensable au microprocesseur, d'une part pour contenir le programme (RAM ou ROM), d'autre part pour contenir les variables (RAM)

Les cases mémoires sont repérées par des adresses, combinaisons binaires codées sur des signaux d'adresses. Un nombre n de signaux d'adresses disponibles sur une ROM détermine une capacité de stockage de 2<sup>n</sup> cases mémoire. Plusieurs composants mémoire peuvent être raccordés aux mêmes signaux d'adresses, aux mêmes signaux de données et aux mêmes signaux de contrôle RD# et WR#. La broche CS# permet d'activer leur fonctionnement dans une plage d'adresses donnée qui leur est spécifique par conception de la logique de décodage.

L'adresse présente sur le bus d'adresses se sépare dans le composant en adresse ligne et adresse colonne. Le décodeur ligne décode l'adresse ligne et sélectionne une ligne de la matrice. Le décodeur colonne décode l'adresse colonne et sélectionne une colonne de l'adresse colonne. La case mémoire située à l'intersection de la ligne et de la colonne sélectionnée est ainsi adressée. Lorsque les signaux CS# d'une part et RD# ou WR# d'autre part sont actifs, un buffer 3 états bidirectionnel met en relation la case mémoire sélectionnée avec le bus de données, dans le sens approprié.

### 1.4.1. Les mémoires vives

Il existe 2 types de mémoire vive les mémoires statiques et les mémoires dynamiques.

La cellule de base (1 bit de mémoire) d'une RAM statique est un bistable. Une telle RAM peut être sauvegardée au moyen d'une batterie ou d'une pile. Certains composants sont même spécialement conçus à cet effet et consomment en stand-by sur leur broche d'alimentation un courant inférieur à  $1~\mu A$ .

La cellule de base (1 bit) d'une RAM dynamique étant une capacité réalisée sur le silicium, la surface occupée sur le silicium est donc sensiblement moins importante que dans le cas d'une mémoire statique.

Les mémoires dynamiques sont donc intéressantes pour réaliser de gros plans mémoire.

En revanche, les courants de fuite des capacités les déchargent en quelques millisecondes. L'information qu'elles contiennent doit donc être lue et réécrite périodiquement avant le délai fatidique. Ces lectures-réécritures sont appelées "rafraîchissements" et sont effectuées pour une ligne complète de la matrice. En quelques millisecondes, c'est donc l'ensemble des lignes qui doit être rafraîchi, afin de revenir à temps à la 1ère ligne rafraîchie.

### 1.4.2. Les mémoires mortes

Une ROM est une mémoire accessible seulement en lecture. Elle ne comporte pas de broche WR#. Un signal RD# (parfois OE#) synchronise la sortie de la donnée mémorisée sur les signaux de données.

14 Architecture des ordinateurs

<sup>&</sup>lt;sup>1</sup> Nous ne parlons pas des processeurs hautes performances qui intègrent sur la même puce un processeur et de la mémoire cache.

Plusieurs composants mémoire peuvent être raccordés aux mêmes signaux d'adresses, aux mêmes signaux de données et au même signal RD#. La broche CS# permet d'activer leur fonctionnement dans une plage d'adresses donnée qui leur est spécifique (voir logique de décodage).

### 1.5. Entrées - sorties

### 1.5.1. Activation des signaux selon l'instruction exécutée

|    | $M/\overline{IO} = 0$   | $M/\overline{IO} = 1$                       |

|----|-------------------------|---------------------------------------------|

| RD | Entrée :<br>IN AL,adrIO | Tout accès en <b>lecture</b> à la mémoire.  |

| WR | Sortie: OUT adrIO,AL    | Tout accès en <b>écriture</b> à la mémoire. |

Des instructions d'entrée et de sortie existent parfois dans le jeu d'instructions d'un microprocesseur. IN et OUT sont les mnémoniques utilisés par Intel pour ses microprocesseurs. On parle alors d'espace adressable séparé pour les entréessorties ou d'adressage IO. Dans ce cas, le microprocesseur fournit et pilote un signal (M/IO#) qui indique à son environnement si l'adresse qu'il génère concerne la mémoire ou au contraire est une adresse IO, c'est-à-dire une adresse d'un registre d'entrée ou de sortie.

Parfois, on doit se servir des mêmes instructions que pour la mémoire. On parle alors d'espace adressable unique. Une partie de cet espace est alors réservé pour les dispositifs d'entrée-sortie, au détriment de l'espace mémoire disponible.

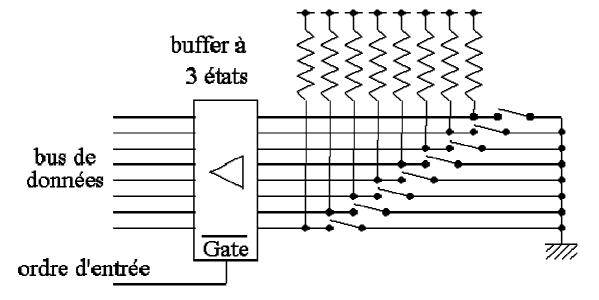

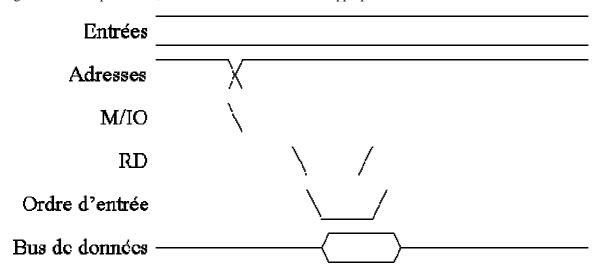

### 1.5.2. Un dispositif d'entrée de base

Ce dispositif élémentaire est un port parallèle très simple figé en entrée. Il donne au microprocesseur un accès à la combinaison binaire codée sur la série d'interrupteurs. Un interrupteur fermé code un 0 (masse), un interrupteur code un 1 logique (Vcc).

Lorsque le microprocesseur accède à ce registre d'entrée, il le fait à une adresse bien précise qu'on appellera ici « l'adresse des interrupteurs ». Le signal appelé ici « ordre d'entrée » provient d'une logique de décodage appropriée et est supposé s'activer (c'est-à-dire passer à 0) lorsque les conditions suivantes sont réunies :

- « l'adresse des interrupteurs » est présente sur le bus d'adresses

- le signal RD# est actif (dans l'état 0)

- le signal M/IO# indique un accès IO (dans l'état 0)

### 1.5.3. Chronogramme d'entrée

Quand le microprocesseur exécutera une instruction IN à l'adresse des interrupteurs, ces conditions seront réunies et l'ordre d'entrée passera à 0, le buffer 3 états propagera l'état des interrupteurs vers le bus de données. Le microprocesseur étant entrain d'exécuter cette instruction IN, un de ses registres est à l'écoute du bus de données et captera l'information. La combinaison binaire codée par les interrupteurs se trouvera donc mémorisée dans un des registres du microprocesseur, ouvrant la voie à un traitement approprié.

C'est ainsi que le microprocesseur peut **connaître son environnement**, qu'il s'agisse des boutons poussoirs d'une montre gérée par un microprocesseur embarqué, qu'il s'agisse de capteurs industriels reliés à un ordinateur de process ou qu'il s'agisse d'un périphérique d'entrée d'un ordinateur, comme un clavier ou une souris, on a recours à un mécanisme similaire.

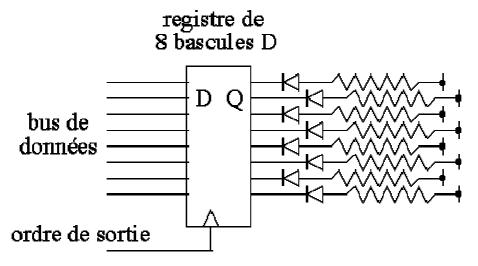

## 1.5.4. Un dispositif de sortie de base

Ce dispositif élémentaire est un port parallèle très simple figé en sortie. Il permet au microprocesseur d'allumer des voyants à led selon une combinaison binaire de son choix. Un 0 (masse) sur une sotie Q du registre D-edge provoquera

une ddp par rapport à Vcc, allumant ainsi le voyant. Un 1 sur une sortie Q annule la ddp relative à Vcc éteignant ainsi le voyant.

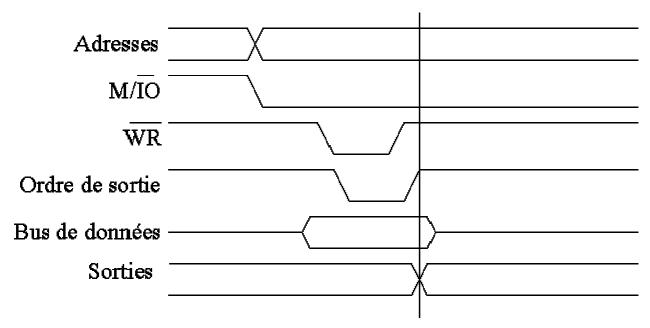

Lorsque le microprocesseur accède à ce registre de sortie, il le fait à une adresse bien précise qu'on appellera ici « l'adresse des voyants ». Supposons qu'une logique de décodage appropriée élabore un signal appelé ici « ordre de sortie » et que cette logique de décodage est conçue de telle façon que l'ordre de sortie s'active (c'est-à-dire passe à 0) lorsque les conditions suivantes sont réunies :

- « l'adresse des voyants » est présente sur le bus d'adresses,

- le signal WR# est actif (dans l'état 0)

- le signal M/IO# indique un accès IO (dans l'état 0)

### 1.5.5. Chronogramme de sortie

Quand le microprocesseur exécutera une instruction OUT à l'adresse des voyants, ces conditions seront réunies et **l'ordre de sortie passera à 0 et sur son front remontant**, l'information présente sur le bus de données sera mémorisée dans le registre D-edge. Le microprocesseur étant entrain d'exécuter cette instruction OUT, l'information présente sur le bus de données est la combinaison binaire d'allumage des voyants que le microprocesseur souhaite écrire.

C'est ainsi que le microprocesseur peut **agir sur son environnement**, qu'il s'agisse des commandes du moteur d'un magnétoscope géré par un microprocesseur embarqué, qu'il s'agisse d'actionneurs industriels reliés à un ordinateur de process ou qu'il s'agisse d'un périphérique de sortie d'un ordinateur comme une imprimante, on a recours à un mécanisme similaire.

Généralement, les dispositifs d'entrée-sortie se présentent plutôt sous forme de circuits intégrés appelés contrôleurs d'entrées-sorties. Ces dispositifs contiennent des registres d'entrée-sortie. Il ne faut pas les confondre avec les registres du processeur.

L'accès aux registres d'entrée-sortie est comparable à l'accès à la mémoire. Il y a cependant une différence importante entre une case mémoire et un registre d'entrée-sortie : quand on a écrit dans une RAM, on relit (normalement) la valeur qu'on vient d'écrire. Quand on écrit dans un registre de sortie à une adresse, **on ne relit généralement pas la même valeur** à cette même adresse. Il s'agit d'ailleurs conceptuellement de registres différents. Par exemple, le registre de données d'un port série est accessible à une même adresse en entrée et en sortie. Mais, en entrée, il contient un caractère que le port série a reçu, tandis qu'en sortie, il contient la donnée que le port série doit émettre.

# 1.6. Fonction décodage

La fonction décodage à pour rôle de sélectionner une barrette ou un boîtier mémoire, un contrôleur d'entrée-sortie parmi plusieurs. En effet, il y a plusieurs boîtiers mémoire (ou plusieurs banques) dans un système, qui sont tous câblé(e)s de la même façon à l'exception d'une broche spécifique : le chip select (ou chip enable). Pour les mémoires et les contrôleurs d'entrée-sortie, cette broche est une entrée qui active leur fonctionnement. Le but de la fonction de décodage est d'activer tel ou tel "chip select" selon la valeur de l'adresse présente sur le bus d'adresses.

La conception de la logique de décodage permet d'établir la **cartographie** d'un système, c'est-à-dire la **correspondance entre une plage d'adresses et une ressource** ou entre une adresse et un registre d'entrée ou de sortie.

L'espace adressable est l'ensemble des adresses qu'un microprocesseur peut générer sur son bus d'adresses. Dans l'espace adressable d'un système, il se peut qu'une plage d'adresses corresponde à de la RAM, de la RAM sauvegardée, de la Flash, à des registres d'entrée-sortie ou à **rien du tout**. Ce dernier cas se produit lorsque aucun dispositif ne voit son chip select activé pour une adresse ou une plage d'adresses donnée.

Il se peut aussi qu'une logique de décodage active une même ressource pour des plages d'adresses différentes.

La logique de décodage peut aussi parfois tenir compte de signaux de contrôle tels que RD#, WR# et M/IO# pour élaborer les chip select des contrôleurs d'entrée-sortie.

Une logique de décodage est généralement purement combinatoire. On peut l'implanter à l'aide de portes logiques, de circuits décodeurs, ou à l'aide de composants programmables.

Les contrôleurs d'entrée-sortie contiennent généralement plusieurs registres. Une logique de décodage intégrée exploitant quelques signaux d'adresses sélectionne les registres à l'intérieur de la plage d'adresses correspondant à leur chip select.

# 1.7. Actions du microprocesseur

| M/IO# | RD# | WR# | Instruction exécutée | Sens de fonct <sup>t</sup> du bus de données | Nom de<br>l'opération |

|-------|-----|-----|----------------------|----------------------------------------------|-----------------------|

| X     | 0   | 0   |                      | impossible                                   |                       |

| 0     | 0   | 1   | IN                   | IO -> μP                                     | entrée                |

| 1     | 0   | 1   | fetch / MOV          | mem -> μP                                    | lecture               |

| 0     | 1   | 0   | OUT                  | μP -> IO                                     | sortie                |

| 1     | 1   | 0   | MOV                  | μP -> Mem                                    | écriture              |

| X     | 1   | 1   | travail interne      | Hi-Z                                         | repos (idle)          |

Ce tableau résume les comportements du microprocesseur et les différents usages du bus de données selon les différentes combinaisons binaires indiquées par le processeur sur ses signaux de contrôle.

# 1.8. Le port série

La notion de contrôleur d'entrée-sortie est illustrée ici par un port série. Les ports série sont parfois connus sous le nom d'UART ou USART (Universal Synchronous/Asynchronous Receiver Transmitter). Leur rôle est le suivant :

- Emission

- conversion parallèle (bus données) série (Tx)

- Réception

- conversion série (Rx) parallèle (bus données)

- Divers modes

- synchrone : synchronisation à chaque trame

- asynchrone : synchronisation à chaque caractère

Les contrôleurs d'entrée-sortie sont de natures très variées. Ils sont plus complexes que les dispositifs d'entrée et de sortie élémentaires étudiés précédemment.

Par exemple, pour une communication série asynchrone (modems) écrire dans le registre de donnée déclenche l'émission du caractère alors que la lecture du registre de donnée fournit le caractère reçu. Écrire dans le registre de configuration définit la vitesse de la transmission, le type de parité (pour la détection d'erreur), le nombre de bits d'arrêt, etc... Lire le registre de configuration donne accès à l'état du port série : un caractère reçu est disponible ou non dans le registre de donnée, une erreur de parité a été détectée, etc...

Dans une liaison série asynchrone, l'unité d'émission est le caractère qui peut être codé sur 5 à 8 bits utiles selon l'ampleur du jeu de caractères à transmettre. Un jeu de caractères à 8 bits autorisera 256 caractères différents.

L'horloge de transmission n'est pas émise sur un signal séparé. La fréquence des transitions est convenue entre l'émetteur et le récepteur et elle est générée par un oscillateur à quartz du côté émetteur comme du côté récepteur. Avant l'émission d'un caractère, il faut donc indiquer que la transmission va commencer, c'est le rôle du bit de start.

- 1. La ligne étant au repos à l'état logique 1, le bit de start sera un 0 à la sortie du port série qui indiquera au destinataire le début de la transmission et lui permettra de retrouver la phase de l'horloge.

- 2. Les bits utiles sont émis à la suite du bit de start. Un bit de parité peut être émis à titre de contrôle d'intégrité des données. Une parité paire est un 1 si le nombre de 1 dans les données utiles est pair. Dans le cas contraire, une parité paire sera un 0. Une parité impaire est un 1 si le nombre de 1 dans les données utiles est impair. Dans le cas contraire, une parité impaire sera un 0. L'émission d'une parité n'est pas obligatoire. L'émetteur et le destinataire doivent en convenir.

- 3. Avant d'émettre le caractère suivant, l'émetteur doit imposer un silence minimal sur la ligne appelé bit stop ou bit d'arrêt. L'état de silence de la ligne est l'état 1. Toujours par convention entre l'émetteur et le destinataire, ce silence aura une durée supérieur ou égal à 1 ou 1,5 ou 2 périodes de l'horloge de transmission. On parlera de 1 bit stop, 1.5 bit stop ou 2 bits stop. Si l'émetteur n'a rien à émettre, il peut maintenir un silence de plus longue durée sur la ligne.

A la sortie du port série, les niveaux sont TTL. Pour s'adapter à une norme électrique tels que V24 ou RS232C, il est nécessaire de recourir à des circuits "drivers" de ligne qui adaptent les niveaux TTL aux niveaux électriques requis par la norme. Les boucles de courant convertissent les niveaux TTL en passage ou non-passage d'un courant plutôt qu'un niveau électrique. Ce type de liaison assure généralement une meilleure immunité au bruit.

Les réseaux d'ordinateurs transmettent les informations de manière synchrone. L'opposition de vocabulaire "synchrone" ou "asynchrone" est assez discutable. La différence est l'unité de transmission et donc les moments où la synchronisation a lieu après un silence. La liaison asynchrone synchronise avant chaque caractère, la liaison synchrone synchronise avant chaque trame. Une trame a une taille de quelques dizaines à quelques milliers d'octets.

### 1.9. Constitution

Un port série est constitué de registres permettant au processeur non seulement d'émettre et de recevoir des données mais aussi de paramétrer son fonctionnement et de connaître son état.

- Registre de commande (write) et d'état (read)

- Registre de données

- à émettre (write)

- reçue (read)

- Registre de commande

- rang de division

- nb de bits de donnée

- nb de bits d'arrêt

- type de parité

- génération d'interruptions

- signaux de service

- Registre d'état

- erreurs, indicateurs

- signaux de service

- Emetteur

- Récepteur

- Pré diviseur

Afin de limiter les risques de perte de données, un double registre de données voir une petite file est parfois présente. Avec le fonctionnement en simple registre de données, une donnée est reçue dans le récepteur constitué d'un registre à

décalage. Quand la donnée est complète, elle est transférée dans le registre de donnée accessible en lecture par le processeur. Si le processeur ne la lit pas suffisamment rapidement, il se peut que le registre de donnée soit écrasé par la réception de la donnée suivante.

### 1.10. Brochage

- Côté microprocesseur

- Quelques signaux d'adresses (sélection des registres)

- chip select

- bus de données

- Côté utilisation

- Tx, Rx : émission, réception (niveau TTL)

- TxClk, RxClk : horloges

- RTS, CTS, DTR, DSR: signaux de service du modem

Ce port série est double : le signal A#/B, relié à un signal d'adresse permet de choisir entre les deux ports série. Le signal C/D# permet de choisir entre l'adresse du registre de commande-état d'une part et le registre de données d'autre part.

|                      | $C/\overline{D} = 0$ | $C/\overline{D} = 1$ |

|----------------------|----------------------|----------------------|

| $\overline{A}/B = 0$ | Données canal A      | Contrôle canal A     |

| $\overline{A}/B = 1$ | Données canal B      | Contrôle canal B     |

Une petite logique de décodage interne élabore les ordres d'entrée et de sortie des registres présents dans un contrôleur d'entrée-sortie. Aussi son brochage comportera-t-il quelques signaux d'adresses (autant que nécessaire pour adresser le nombre de registres qu'il renferme) mais aussi les signaux RD# et WR# et bus de données. Il comportera également un ou plusieurs chip select. Selon le type d'accès (espaces adressables séparés ou espace unique) le chip select sera activé en tenant compte ou non d'un signal de type M/IO#.

Les contrôleurs d'entrée-sortie comportent aussi des signaux spécifiques à leur fonction : signaux d'émission et de réception pour un port de communication, détection de collision pour un port ethernet, etc...

## 1.11. Microcontrôleur

Un microcontrôleur, ou microprocesseur embarqué, associe sur une même puce, plusieurs dispositifs :

- Microprocesseur + RAM + ROM + dispositifs d'entrées-sorties

- Multiples entrées d'interruptions<sup>2</sup> internes et externes

- Choix selon ressources nécessaires

- Se programme comme une ROM

- Adapté aux "petits systèmes" 8, 16, 32 bits

Outre des dispositifs d'entrée-sortie, un microcontrôleur intègre un microprocesseur et de la mémoire RAM, ROM, éventuellement Flash ou EEPROM.

20 Architecture des ordinateurs

.

<sup>&</sup>lt;sup>2</sup> Les interruptions seront étudiées dans le chapitre consacré à la gestion des entrées-sorties.

Un microcontrôleur est conçu pour exécuter des programmes orientés entrée-sortie, c'est-à-dire tenant compte des informations lues sur les registres d'entrée pour écrire dans les registres de sortie. Les premières applications des microcontrôleurs faisaient appel à des programmes simples. Ils pouvaient se passer de système d'exploitation et être écrits en assembleur. Mais comme toujours dans le domaine de la technologie, l'ambition des ingénieurs a augmenté avec les années, et le besoin de petits systèmes d'exploitation s'est fait sentir, notamment pour gérer l'exécution apparemment simultanée de plusieurs programmes. L'interface utilisateur fait de plus en plus facilement appel à un écran graphique, ce qui fait ressembler les programmes des microcontrôleurs à ceux des ordinateurs.

On parle d'informatique embarquée ou enfouie. C'est un domaine qui a le vent en poupe, avec l'explosion du marché des téléphones portables, de l'informatique nomade, et autres produits grand public à fort volume de vente.

Certaines réactions du microcontrôleur doivent intervenir dans un délai garanti, comme pour un système ABS de voiture. Dans ce cas, on a généralement recours à un système d'exploitation ou noyau temps-réel.

# 2. Le matériel : travail dirigé

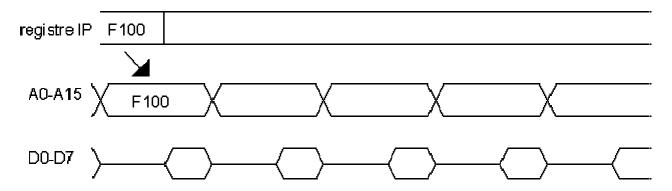

# 2.1. Déroulement d'une séquence d'instructions

Imaginez l'activité sur le bus d'adresses et le bus de données lorsqu'un processeur accède en lecture à une case mémoire en lecture. Pour fixer les idées, disons qu'il s'agit d'un processeur 8 bits ayant un bus d'adresses de 16 bits. L'instruction effectuée est la suivante.

Adresse Code machine Code assembleur

F100 A07CF3 mov al,[F37C]

Adressage direct

On suppose également que les informations stockées en mémoire respectent l'ordre poids faible puis poids fort.

1. Complétez le chronogramme suivant.

2. Quelles sont les différentes informations qui circulent sur le bus de données ?

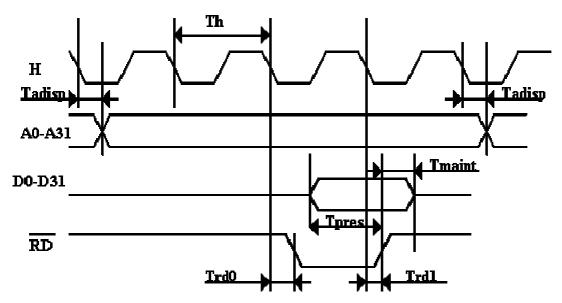

# 2.2. Chronogramme de lecture

$La \ fiche \ technique \ d'un \ microprocesseur \ comporte \ le \ chronogramme \ de \ lecture \ suivant. \ Observer:$

- 1. A quoi voit-on qu'il s'agit d'un chronogramme de lecture ?

- 2. Combien de périodes de l'horloge H y a-t-il pour le transfert d'un mot ?

- 3. Quelle est la taille de ce mot ?

- 4. Le constructeur précise également que deux octets consécutifs en mémoire sont distants de 1 dans l'espace adressable. Quelle est la taille de l'espace adressable ?

# 2.3. Performances des processeurs

La fiche technique fournit également les durées suivantes.

| Temps  | Signification      | Min.  | Max.  |

|--------|--------------------|-------|-------|

| Th     | Période d'horloge  | 50 ns |       |

| Tadisp | Adresse disponible | 7 ns  | 10 ns |

| Trd0   | Read à 0           | 8 ns  | 10 ns |

| Trd1   | Read à 1           | 7 ns  | 10 ns |

| Tpres  | Préselection       | 30 ns |       |

| Tmaint | Temps de maintien  | 5 ns  |       |

### Questions

- 1. Quelle est la fréquence maximale à laquelle ce processeur peut fonctionner ?

- 2. Calculer en octets par seconde le débit possible sur le bus de ce microprocesseur à la fréquence maximale du microprocesseur.

- 3. Sachant que le nombre moyen d'instructions exécutées par période de l'horloge H est de 0,22 calculer la puissance moyenne de ce processeur.

### 2.3.1. Temps imposé à la mémoire par le microprocesseur

Des mémoires de 50 ns de temps d'accès sont reliées directement au bus de ce microprocesseur. Le processeur imposant à la mémoire le rythme des accès, au-delà d'une certaine fréquence de fonctionnement, la mémoire ne répondra pas suffisamment vite.

### Questions

- 1. A quel instant les données en provenance de la mémoire doivent-elles être présentes sur le bus de données du processeur pour que la lecture s'effectue correctement ?

- 2. A quel instant la mémoire "voit-elle" démarrer le cycle de lecture ?

- 3. Calculer le temps d'accès imposé par le processeur fonctionnant à sa fréquence maximale ?

- 4. Quel temps d'accès la mémoire peut-elle tenir ?

- 5. A quelle fréquence maximale peut-on faire tourner le microprocesseur pour que les mémoires puissent tenir le temps d'accès imposé par le processeur ?

### 2.3.2. Overhead du système d'exploitation, puissance utile

Le système d'exploitation utilise pour son propre compte une partie du temps CPU, ceci réduit d'autant la puissance disponible pour les applications. Le terme "overhead" désigne le pourcentage du temps ou de puissance consommée par le système d'exploitation. Cette charge est du reste variable au cours du temps selon le type de situation auquel il a à faire face. On parle donc d'overhead moyen ou de pointe.

### Questions

1. Quelle est la puissance utile minimale dont disposent les applications, si le système d'exploitation consomme en pointe 10% de la puissance CPU.

### 2.3.3. Durée des entrées - sorties

Le port série est le dispositif de communication asynchrone utilisé dans les modems. Il est chargé d'émettre sous forme série les données d'un programme et de paralléliser les données reçues sous forme série. Le processeur est ainsi libéré de cette tâche. L'horloge n'est pas émise sur un signal séparé. Le rythme de transmission doit être convenu entre l'émetteur et le récepteur et généré de chaque côté.

- 1. On parle de liaison série asynchrone. Pourquoi utilise-t-on ce terme ? A quelles occasions y a-t-il synchronisation ?

- 2. Que signifie 1,5 bit d'arrêt ? Peut-on couper un bit en 2 ?

- 3. A quoi correspond la notion de bit d'arrêt ?

- 4. Quels sont les paramètres relatifs à la parité côté émetteur ? côté récepteur ?

- 5. Qu'est-ce qu'une parité paire ? une parité impaire ?

- 6. On considère une liaison à 9600 bps, 8 bits de données utiles, 2 bits d'arrêt, parité paire.

- 7. Quel est le temps minimum qui s'écoule entre le début d'émission d'un caractère et le début d'émission du suivant ?

- 8. On utilise un sous-programme qui prend en charge l'émission d'un tampon de mémoire de 20 octets. Calculer le nombre d'instructions que cela représente pour un processeur 50 Mips ?

# 3. Le logiciel : modèle de programmation

Les principaux concepts liés à l'assembleur seront présentés de la façon la plus générale possible; cependant, les exemples donnés feront appel au jeu d'instructions de la famille 86 d'Intel.

# 3.1. Organisation de la mémoire

Bien que le 8086 ait un bus de données 16 bits, il lui est quand même possible d'adresser des octets. Ainsi, avec ses 20 bits d'adresses, il lui est possible d'adresser 1 Mégaoctet sous forme d'octets ou sous forme de mots de 16 bits. La terminologie employée est la suivante :

octet: 8 bits, mot: 16 bits, double mot: 32 bits.

Deux octets situés à des adresses consécutives constituent un mot. Quatre octets (ou deux mots) consécutifs constituent un double mot. Les types d'accès à la mémoire générés par le microprocesseur sont soit des accès par octet, soit des accès par mot.

Supposons que la mémoire contienne les octets 5F, A3, 3C, 24 et 32 stockés à partir de l'adresse n

@n:5F

@n+1:A3

@n+2:3C

@n+3:24

@n+4:32

Intel utilise le stockage dit "little-endian" alors que Motorola utilise le stockage "big-endian". Comme ce cours est illustré avec des processeurs Intel, voyons en quoi consiste le stockage "little-endian".

Un accès mot à l'adresse n lira en fait les octets consécutifs 5F et A3. L'ordre "little-endian" considère que le poids faible 5F correspond à l'adresse la plus faible n. On peut alors dire que le mot stocké à l'adresse n est A35F. De la même façon, on aura les mots suivants :

@n: A35F@n+2: 243C

Un accès mot à l'adresse n+1 donnerait 3CA3, mais 3C et A3 correspondent aux mêmes cases mémoires que celles utilisées dans les mots A35F et 243C. Si le 8086 est capable de générer 2<sup>20</sup> adresses différentes, cela signifie qu'il est capable d'adresser 2<sup>20</sup> octets soit 1 Mo.

Un accès par double mot à l'adresse n lira les octets 5F, A3, 3C et 24. Le stockage little-endian considère que le poids le plus faible est 5F et que le poids le plus fort est 24. On peut alors dire que le double mot stocké à l'adresse n est 243CA35F. Un accès double mot à l'adresse suivante fera apparaître 3 octets commun à ce mot :

@n:243CA35F@n+1:32243CA3

La granularité dans l'inversion des poids est l'octet car les adresses sont en général des adresses d'octets.

Cette différence dans l'ordre de stockage pourrait poser des problèmes d'interopérabilité pour des machines reliées en réseau. En fait, c'est le réseau qui impose un ordre commun. La couche "présentation" de chaque machine est chargée d'adapter les informations transmises à l'ordre du réseau et celles reçues à l'ordre de la machine. TCP/IP et les autres protocoles d'Internet sont généralement big-endian.

-

<sup>&</sup>lt;sup>3</sup> Cette allusion aux Voyages de Gulliver insiste sur l'aspect purement arbitraire de ce choix. Une traduction de cette fiction emploie les termes "petit-boutiens" et "gros-boutiens". Ces deux peuples se livraient une guerre sans merci, car ils n'étaient pas d'accord sur le côté par lequel ouvir les œufs qu'ils consommaient.

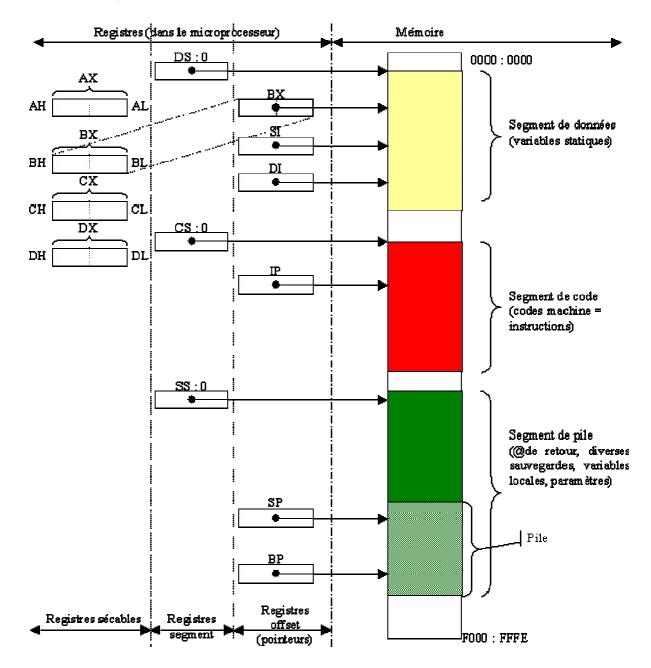

# 3.2. Le modèle de programmation

Certains **registres** du microprocesseur sont **accessibles au programmeur** par l'emploi des instructions appropriées. Du point de vue du programmeur le microprocesseur représente des **instructions** mais également un certain nombre de registres et de **mémoire**. Tout cela constitue le **modèle de programmation** du microprocesseur.

On peut distinguer deux types de registres : ceux qui servent pour mémoriser les opérandes des opérations et ceux qui sont là pour des raisons plus techniques comme le contrôle de l'exécution du programme ou la gestion des zones de mémoire.

Pour accéder aux registres, il n'est pas besoin d'adresse, il suffit de citer le nom du registre dans l'instruction. Ceci est le résultat du codage spécifique de l'instruction en une valeur numérique unique : le code machine. En fait, le registre à utiliser est codé sur un certain nombre de bits du mot constituant l'instruction. Ceci est également possible à cause de la **situation privilégiée des registres** au cœur du microprocesseur, en relation directe avec les autres éléments constituants.

Les registres sont caractérisés par leur **nom** bien sûr, mais également par leur **taille** et leur **rôle**. Les rôles principaux dévolus aux registres sont la **manipulation des données** et l'**adressage**, c'est-à-dire l'accès aux données en mémoire. Enfin, on trouve des registres plus particuliers ou qui en plus de leur utilisation traditionnelle ont un **comportement particulier** avec certaines instructions.

### 3.2.1. Modèle de programmation du 8086

Pour la famille 86 des processeurs INTEL, le modèle de programmation comprend les registres suivants :

AX, BX, CX, DX sont quatre registres de 16 bits également accessibles par demi-registres de 8 bits : AH, AL, BH, BL, CH, CL, DH, DL. Les suffixes H et L signifient "High" et "Low". Ces registres permettent de manipuler des données. De plus, BX peut aussi servir de registre d'adresse.

Les registres d'adresses sont employés lors des opérations d'adressage, c'est-à-dire l'accès à la mémoire externe. Tous les registres comportant le mot "pointer" sont des registres d'adresses :

- On trouve bien sûr le pointeur d'instructions IP (Instruction Pointer) encore appelé PC (Program Counter)

- Le registre SP (Stack Pointer) autorise la manipulation de la pile des appels de sous-programmes.

- Le registre BP (Base Pointer) permet d'accéder aux éléments de la pile autrement que par son sommet.

Il en va de même pour les registres comportant le mot index :

• Les registres SI (Source Index) et DI (destination Index) sont des registres autorisant l'adressage indirect.

Les registres BX, SI, DI et BP sont des registres d'adresses utilisés pour adresser les variables manipulées par les programmes. Les autres registres d'adresses comme SP et IP ont un rôle plus technique qui sera explicité.

Les registres de segment sont des registres ayant un rôle typiquement technique : ils permettent de distinguer des zones de mémoire selon les usages qu'on en fait. On distingue les segments de code (CS = Code Segment contenant les instructions), les segments de données (DS = Data Segment), les segments de pile (SS = Stack Segment). Les registres de segments CS, DS et SS repèrent à un instant donné, la position respective des segments de code, de données et de pile. Un registre segment supplémentaire (ES = Extra Segment) repère au besoin un deuxième segment de données.

On trouve également le mot d'état (FLAGS) qui est un registre regroupant comme son nom l'indique différents **indicateurs** (drapeaux) sur l'état du microprocesseur à la suite de l'exécution d'une instruction. L'exemple le plus évident est l'indicateur de retenue (CARRY), utile notamment pour l'addition, qui occupe un bit du registre FLAGS. Dans la description du fonctionnement de chaque instruction, on indique comment sont affectés les divers indicateurs.

Les indicateurs arithmétiques sont les suivants :

- CF (Carry Flag): retenue pour l'addition ou pour la soustraction,

- AF (hAlf carry Flag): retenue pour le quartet de poids faible,

- ZF (Zero Flag): indique un résultat nul (quand il est positionné à 1 !!!),

- SF (Sign Flag): indique un résultat négatif (recopie du bit de poids fort du résultat),

- PF (Parity Flag) : indique que le nombre de bits 1 dans l'octet de poids faible du résultat est pair,

- OF (Overflow Flag) : indique un dépassement de capacité de l'opération.

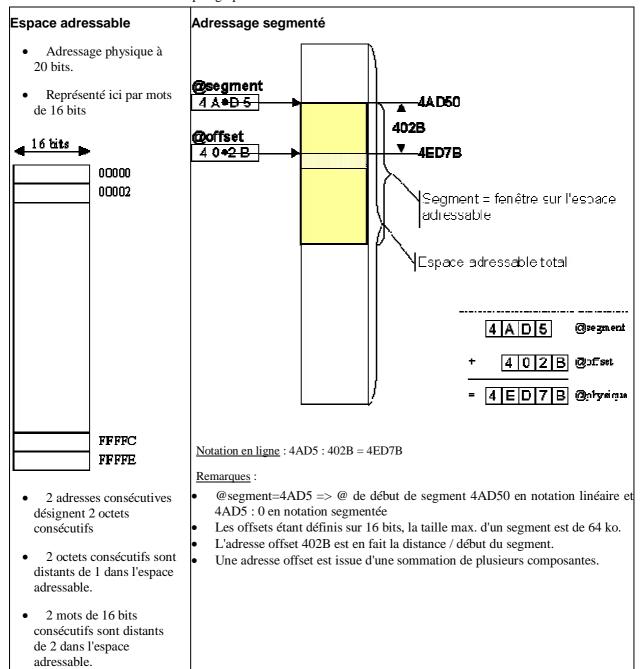

### 3.3. Segmentation du 8086

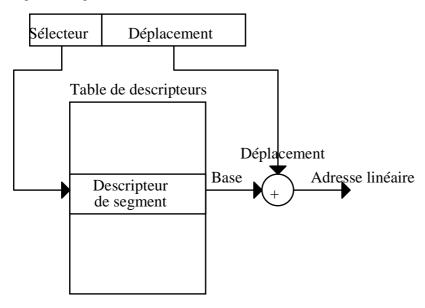

Nous présentons ici le modèle de segmentation de la famille Intel 8086. La segmentation du 386, plus évoluée est présentée plus loin dans les aspects relatifs aux systèmes d'exploitation.

### 3.3.1.1. Définition

La segmentation est une façon que le microprocesseur a d'adresser et de voir la mémoire. Le microprocesseur 8086 comporte 20 bits d'adresse, sa capacité d'adressage est donc d'un Mégaoctet. Cependant, les registres ne comportant que 16 bits pour des raisons historiques, la manipulation d'adresses 20 bits n'est donc normalement pas possible.

L'analyse des valeurs d'adresses permet d'établir que les **accès** aux instructions sont pendant un quantum de temps, **localisés** pour la plupart d'entre eux dans une zone d'adressage limité. Plus les accès sont lointains, plus ils sont rares. Les concepteurs du 8086 ont donc fait le pari que l'on pouvait travailler implicitement avec des adresses 16 bits la plupart du temps, et que la manipulation (explicite) d'adresses 20 bits étant plus rares pouvaient faire l'objet d'un mécanisme plus complexe.

C'est ce mécanisme qui porte le nom de **segmentation**. Il fait appel à des **registres de segment** contenant une composante de l'information d'adresse qui change peu (*composante continue*) et aux **registres d'adresses offsets** qui contiennent en quelque sorte la *composante variable* de l'information d'adresse. Les registres BX, SI, DI, SP, BP, IP sont des registres d'adresses offsets.

Comme le microprocesseur utilise **plusieurs flots d'adressage** (un pour le programme, un pour la pile, et un ou deux pour les données), **plusieurs registres segments** sont nécessaires. En effet, le 8086 comporte effectivement un registre segment pour le code (CS : Code Segment), un registre segment pour la pile (SS : Stack Segment) et deux registres de segment pour les données (DS : Data Segment et ES : Extra Segment).

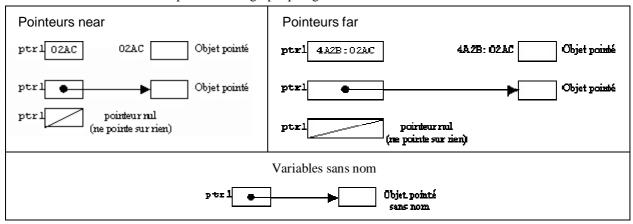

Certaines instructions manipulent seulement la partie offset, d'autres manipulent la partie offset et la partie segment. Il y a deux types d'adresses : les adresses "near" ou adresses offset, codées sur 16 bits et les adresses "far" ou adresses segmentées, codées sur 32 bits, c'est-à-dire comportant une partie segment et une partie offset. Il existe donc des pointeurs near occupant 16 bits en mémoire et des pointeurs far occupant 32 bits en mémoire. Les sous-programmes (les équivalents assembleur des procédures / fonctions des langages évolués) étant repérés par des adresses peuvent être des sous-programmes near ou des sous-programmes far.

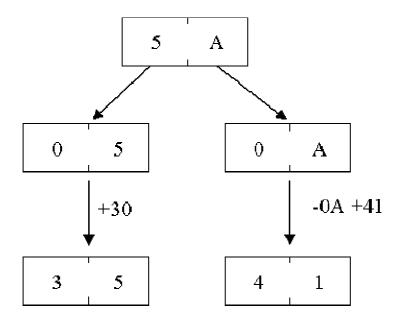

### 3.3.1.2. Calcul de l'adresse

L'adresse physique, celle qui circule sur le bus d'adresses résulte d'un calcul mettant en œuvre une partie segment codée sur 16 bits provenant généralement d'un registre segment et une partie offset également codée sur 16 bits.

$ADR_{20bits} = partie\ segment_{16bits} * 16 + partie\ offset_{16bits}$

On peut remarquer que multiplier par 16 décimal consiste à décaler de 4 bits vers la gauche la partie segment soit d'ajouter un 0 à droite en hexadécimal, le résultat comporte donc 20 bits soit 5 digits hexadécimaux. En rajoutant la partie offset, on peut atteindre 21 bits mais de tels calculs d'adresses ne sont pas souhaitables et le résultat est tronqué à 20 bits. Un segment peut comporter **64 ko** au maximum : la composante variable est exprimée sur 16 bits. Le début du segment correspond à un offset 0 et la fin du segment correspond à l'offset FFFF exprimé en hexadécimal. Un segment ne peut donc commencer qu'à une adresse multiple de 16. Une telle adresse, exprimée en hexadécimal se termine par un 0. Une telle adresse est appelée frontière de paragraphe. Une zone de 16 octets s'appelle en effet un **paragraphe**. Un segment comporte donc au moins **16 octets**. Le paragraphe est l'unité de granularité du segment et les segments commencent sur des frontières de paragraphes.

### 3.3.2. Inconvénients

En introduisant le mécanisme de segmentation, les concepteurs du 8086 ont malheureusement **compliqué** sa programmation. La compréhensibilité du jeu d'instructions s'en trouve également réduite.

De plus, les segments ont une taille maximale fixe de 64 ko. Or, la propriété de localité d'exécution des programmes n'est pas applicable aux données. Prenons le cas de l'accès aléatoire à un tableau de données. Si le **tableau** fait moins de 64 ko, tout va bien, il suffit d'attribuer un registre segment pour le tableau et les accès seront tous dans le segment. Si le tableau fait **plus de 64 ko**, comme l'accès est aléatoire, les instructions doivent remettre en cause a priori le contenu du **registre segment** et donc le **recalculer** à chaque accès.

Dans la plupart des langages évolués, certaines restrictions du 8086 sont réellement contraignantes :

- Un tableau ne peut excéder 64 ko.

- Une variable (même dynamique) ne peut excéder 64 ko.

- La pile est limitée à 64 ko.

La limitation de la pile sera particulièrement sensible pour l'utilisation de la récursivité qui fait un usage important et systématique de la pile.

Avec l'architecture segmentée du 386, toutes ces contraintes disparaissent car les segments ont une taille maximale de 4 Go.

### 3.3.3. Avantages

Parmi les avantages qu'offre la segmentation, on citera la **compacité du code** obtenu à condition que le compilateur ne génère pas du code qui recalcule systématiquement le contenu des registres de segment.

#### Remarque préalable :

L'emplacement exact où sera logé un programme en mémoire vive pour y être exécuté, n'est pas figé. Une partie du système d'exploitation est chargée de trouver de la place. L'emplacement s'exprime en termes d'adresses et on comprend alors que ces adresses ne sont connues qu'au moment du **chargement** en mémoire, juste avant l'exécution. La qualité qu'a un programme de pouvoir s'exécuter à un endroit de la mémoire qui n'est pas connu avant ce moment s'appelle la **relogeabilité**.

Un des avantages de la segmentation est de **faciliter le relogement** des programmes. Le relogement d'un exécutable concerne le code, la pile et les données. Les adresses offsets sont déterminées lors de la production du programme exécutable. L'adresse segment est déterminée lors du chargement en mémoire vive.

Dans le cas idéal de programme où on n'a jamais à remettre en cause le contenu des registres de segment, le programme chargeur n'a qu'à définir le contenu des registres de segment une fois pour toutes.

En dehors du cas idéal, les programmes comporteront généralement plusieurs segments avec des instructions faisant des références entre segments. Ceci oblige à employer des instructions de chargement des registres de segment avec des adresses complètes.

# 3.4. Représentation à la Turbo-Debugger

La mémoire peut être représentée de différentes façons par les outils de mise au point (débogueurs). On peut la représenter en tant que données ou en tant qu'instructions. Dans tous les cas, la colonne de gauche précise à quelle adresse est situé le premier mot représenté sur la ligne. Dans le cas du 8086, l'adresse est représentée sous sa forme segmentée. La partie segment à gauche est séparée de la partie offset à droite par un double point. Il se peut que la partie segment soit celle contenue dans un registre. Dans ce cas, le nom du registre est affiché à la place de la valeur numérique.

### 3.4.1. Représentation de la mémoire en tant que données

Dans la représentation en tant que données, on a le choix entre une représentation par octets et une représentation par mots de 16 bits. Dans la représentation par octets, les données sont affichées en hexadécimal et en ascii lorsqu'un caractère affichable existe. Il s'agit de 2 représentations des mêmes données.

| Adresses  | Octets en hexa Octets en ascii |  |  |

|-----------|--------------------------------|--|--|

| ds:0000   | 73 61 6C 75 74 00 20 20 salut  |  |  |

| Adresses  | Mots de 16 bits en hexa        |  |  |

| 53DC:0000 | 6173 756C 0074 2020            |  |  |

Dans la représentation par mots, deux octets consécutifs sont groupés et remis dans l'ordre naturel qui est opposé à l'ordre de stockage en mémoire qui est l'ordre little-endian pour les processeurs Intel.

### 3.4.2. Représentation de la mémoire en tant qu'instructions

Les outils de mise au point représentent les instructions de deux façons : sous la forme numérique des codes machine d'abord, sous la forme symbolique des codes assembleur ensuite. Il s'agit de 2 représentations des mêmes instructions.

| Adresses                      | Codes machine | Codes assembleur                        |

|-------------------------------|---------------|-----------------------------------------|

| cs:0100<br>cs:0103<br>cs:0106 | вв0200        | mov ax,0001<br>mov bx,0002<br>add ax,bx |

### 3.4.3. Assembleur en ligne de Turbo-C++

Les assembleurs existent en tant qu'outils indépendants de traduction d'une syntaxe "langage d'assemblage" vers des fichiers objets puis vers un fichier exécutable en utilisant un éditeur de liens traditionnel. Les fichiers sources assembleur comportent, non seulement des instructions en langage d'assemblage, mais aussi des déclarations de données et de constantes, avec une syntaxe propre.

Une autre approche de l'assembleur consiste à inclure du code assembleur dans un programme écrit en langage évolué. Les compilateurs C/C++ de Borland permettent d'inclure du code assembleur dans du code C/C++. On parle d'assembleur en ligne ou inline. Le langage C est un langage à structure de bloc. Un bloc en langage C est délimité par des accolades. Borland introduit un nouveau type d'instructions et de blocs préfixé par le mot-clé asm (assembler). Ainsi, il est possible d'entrer une instruction assembleur dans un code C en le préfixant par asm :

```

asm mov ax,1

```

De la même façon, on peut définir un bloc asm :

Pour la définition des constantes et des variables, on a recours au langage C et on peut les manipuler en langage d'assemblage :

```

#define NULL 0

int maVar;

...

asm {

mov ax,NULL

mov maVar,ax

...

}

```

L'avantage est que les données sont typées, contrairement à ce qui se passe avec les syntaxes assembleur. De la même façon, on utilise les étiquettes du langage C qu'on référence par les instructions de sauts et de sauts conditionnels du

langage d'assemblage. L'inconvénient de cette technique est une certaine lourdeur introduite par la nécessité de fermer le bloc asm pour définir une étiquette en C et de rouvrir ensuite le bloc asm comme dans l'exemple suivant :

Les variables locales et les paramètres peuvent aussi être référencés par les instructions assembleur. Dans ce cas, l'assembleur traduit l'instruction par un adressage basé sur BP comme on doit le faire pour ce type de variable. Ceci sera étudié dans le chapitre consacré aux paramètres et variables locales :

```

void proc1( int param1 )

{

int varLoc1;

asm {

mov ax,param1; // traduit par un adressage basé sur BP

mov varLoc1,ax; // idem

}

...

}

```

# 3.5. Association par défaut des registres de segment

Les registres de segment sont prévus pour travailler de concert avec les registres d'adresses offset. Il existe même des **associations par défaut** pour ces collaborations entre registres classiques et registres de segment.

Certaines **associations** sont **naturelles** : le registre IP (pointeur d'instructions) est ainsi associé au registre du segment de code CS. De même, le registre du segment de pile SS est associé aux registres SP et BP prévus pour adresser la pile.

Pour les données, le mode d'adressage, déterminera le registre de segment concerné. En fait, la **règle générale** spécifie que c'est DS qui est utilisé avec les registres BX, SI et DI.

Avec l'adressage basé et indexé, le segment associé par défaut est celui normalement associé avec le **registre de base**, c'est-à-dire soit BX soit BP. Le registre segment SI ou DI n'intervient plus dans ce cas dans le choix du registre de segment associé. BP étant un registre pour adresser la pile, l'adressage basé sur BP avec ou sans indexation utilisera le registre du segment de pile SS. L'adressage basé sur BX avec ou sans indexation utilisera le registre du segment de données DS.

# 3.6. Méthodologie

Afin de ne pas perdre les bonnes habitudes de programmation structurée, vous êtes invités à respecter la méthode suivante :

- 1. vous écrivez une ligne de "programme" en pseudo-langage,

- 2. vous la mettez en commentaire,

- 3. vous écrivez **au-dessous** de cette ligne les instructions assembleurs qui font ce que dit le commentaire, rien de plus, rien de moins.

### 3.6.1. Du bon usage des commentaires

Les commentaires isolés sur une ligne sont des commentaires de spécification : ils disent ce qu'est censé faire le code assembleur qui le suit. Ils doivent permettre la compréhension globale de ce qui est réalisé par le code assembleur. Pour cela, le lecteur n'est censé lire que ce type de commentaires en faisant abstraction des commentaires de fin de ligne.

Les commentaires de fin de ligne sont des commentaires d'implantation. Ils doivent normalement concerner des particularités ou des difficultés relatives au codage en assembleur. Ils pallient la pauvreté sémantique du langage d'assemblage.

# 4. Représentation des données

# 4.1. Les modes d'adressage

Une des activités importante que permette un microprocesseur est l'accès aux données. La *façon d'accéder aux données* est une notion importante pour l'implantation des algorithmes. On emploie le terme de **mode d'adressage**. On emploie un mode d'adressage plutôt qu'un autre en fonction des informations connues au moment de l'assemblage. Certaines informations ne seront connues qu'au moment de l'exécution.

# 4.2. L'adressage immédiat

Si l'opérande lui-même est connu lors de la compilation, alors on peut employer l'adressage immédiat. Celui-ci consiste à spécifier l'opérande directement dans le code machine donc dans le segment de code.

```

#define INCR 1

int iFill;

...

//étiquette opérateur opérandes commentaires

asm {

MOV AL,5; // 5 : adressage immédiat

ADD AX,INCR // INCR : adressage immédiat

MOV BX,offset iFill //offset iFill adressage immédiat

...

```

Dans un langage évolué, l'adressage immédiat correspond à l'utilisation de constantes. Ici l'opérande est la constante 5, qu'on charge dans le registre AL. De même, cette constante peut être symbolique. Dans le deuxième exemple, l'opérande est la constante INCR équivalente à la valeur 1. On l'utilise dans l'instruction d'addition dans le registre AX. Enfin, dans le troisième exemple, l'opérande n'est pas une variable mais l'adresse d'une variable. L'adresse offset des variables réservées par le compilateur peut être connue grâce au mot-clé offset suivi du nom de la variable.

# 4.3. L'adressage direct

Si l'opérande lui-même n'est pas connu lors de la compilation, on ne peut pas utiliser l'adressage immédiat; l'opérande doit alors être stocké dans une variable. Si l'adresse de l'opérande est connue lors de la compilation, alors on peut utiliser l'adressage direct. Celui-ci consiste à spécifier l'adresse de l'opérande dans les instructions du programme.

```

#define INCR 1

int iFill;

...

//étiquette opérateur opérandes commentaires

asm {

MOV AX,[iFill]

...

```

Notons que, contrairement à l'exemple précédent, c'est ici la valeur et non l'adresse de la variable iFill qui est l'opérande de l'instruction. C'est cette valeur qu'on charge dans AX.

L'adressage direct est normalement reconnaissable aux crochets entourant le nom ou l'adresse de la variable. Cependant, les crochets, bien que conseillés, ne sont pas obligatoires. Ainsi, dans l'exemple suivant, la syntaxe des deux instructions mov est la même : les crochets de l'adressage direct autour de iFill sont absents. Le compilateur/assembleur ayant compilé les déclarations de INCR et iFill, il est capable de voir s'il s'agit d'une variable (globale) ou d'une constante, quand il rencontre une instruction manipulant ces identificateurs. La manipulation de la valeur d'une constante fait appel à l'adressage immédiat. La manipulation du contenu d'une variable globale, même en l'absence de crochets, fait appel à l'adressage direct.

# 4.4. L'adressage indirect

Si l'adresse de l'opérande n'est pas connue lors de la compilation, on ne peut pas utiliser l'adressage direct ou plus précisément l'adressage indirect par registre. Il faut alors indiquer au microprocesseur un registre qui contiendra l'adresse de l'instruction au moment de l'exécution. Une ou plusieurs instructions préliminaires récupèrent dans le registre d'indirection (BX, BP, SI ou DI), l'adresse de l'opérande peu importe comment.

Puis, on met en œuvre l'adressage indirect. L'adresse de l'opérande à manipuler n'étant pas connue lors de la compilation, on indique au processeur que cette adresse est située dans tel ou tel registre d'adresse.

Dans un langage évolué, ce type d'adressage correspond à l'utilisation des variables dont l'adresse n'est pas connue lors de la compilation. C'est le cas des variables allouées dynamiquement, par une instruction malloc par exemple. On peut aussi utiliser ce mode d'adressage pour agir sur une diversité de variables : c'est ce qu'on fait dans les procédures et fonctions comportant des paramètres où l'adresse n'est connue qu'au moment du passage des arguments.

L'adressage direct change de nom selon le registre qu'on emploie. Si on utilise un registre de base comme BX ou BP, on parlera d'adressage basé, ou plus précisément d'adressage basé sur BX ou basé sur BP. Si on utilise un registre d'index comme SI ou DI, on parlera d'adressage indexé ou plus précisément d'adressage indexé par SI ou indexé par DI. Quel que soit le nom utilisé, le mécanisme est rigoureusement le même.

D'autre part, rappelons que ces registres d'adresses contiennent des adresses offsets et qu'ils sont implicitement associés à un registre de segment, donc à un segment. Par défaut, [BX], [SI] et [DI] sont utilisés pour accéder au segment de données repéré par DS, tandis que [BP] est utilisé pour accéder au segment de pile repéré par SS.

L'adressage indirect possède aussi plusieurs variantes :

- l'adressage indirect avec déplacement,

- l'adressage basé et indexé,

- l'adressage basé et indexé avec déplacement.

## 4.4.1. L'adressage indirect avec déplacement

L'adressage indirect avec déplacement accède à un opérande dont l'adresse est connue relativement à une autre adresse contenue dans un registre de base ou d'index. La distance entre l'adresse contenue dans le registre et l'adresse de l'opérande sera appelée déplacement (pour ne pas surcharger le mot offset) Le déplacement est connu lors de la compilation et codé dans l'instruction vient s'ajouter à l'adresse présente dans le registre.

```

// déclarations

int iaTab[26];

// instructions

// iaTab[2] = 0;

asm {

mov si,offset iaTab // offset iaTab : adressage immédiat

mov [si+4],0 // [si+4] : adr. indexé avec déplacement

...

```

Dans cet exemple, l'adresse de iaTab[2] est située à 4 octets de distance du début du tableau iaTab car chaque case mémorise un entier, codé sur 2 octets.

On parlera également d'adressage basé avec déplacement avec les registres BX et BP et d'adressage indexé avec déplacement avec SI et DI.

## 4.4.2. L'adressage basé et indexé

L'adressage basé et indexé est un adressage indirect qui met en œuvre deux registres. C'est la somme de ces deux registres qui donne l'adresse de l'opérande : [BX+SI] par exemple. A cause de la structure interne du processeur, il est impossible d'utiliser conjointement BX et BP. De même, il est impossible d'utiliser conjointement SI et DI. Ainsi, les notations [BX+BP] et [SI+DI] sont illégales. Pour que les programmeurs s'y retrouvent dans les combinaisons de registres légales ou illégales, Intel a introduit une distinction entre "registres de base" et "registres d'index". Comme on l'a vu sous la rubrique sur l'adressage indirect, cette distinction est de pure forme : l'adressage indexé et l'adressage basé sont en fait deux noms différents pour un même mécanisme. Les seules combinaisons légales de registres font appel à un registre de base et un registre d'index : [BX+SI], [BX+DI], [BP+SI] et [BP+DI]. Les deux premières combinaisons adressent le segment de données et les deux suivantes adressent le segment de pile.

```

// déclarations

int iaTab[26];

int i;

// instructions

// iaTab[i] = 0;

asm {

bx,offset iaTab

// offset iaTab : adressage immédiat

mov

// [i] : adressage direct

si,[i]

mov

// si = si+si = si*2

add

si,si

[bx+si],0

// [bx+si] : adr. basé+indexé

mov

```

Ce code n'a qu'un but pédagogique. En fait, l'adresse offset de iaTab est ici connue au moment de la compilation. On pouvait donc se passer de l'adressage basé et indexé et se contenter d'un adressage indexé avec déplacement en remplaçant alors [bx+si] par [si+iaTab] (pas besoin de mettre offset devant iaTab).

Dans un langage évolué, ce mode d'adressage correspond à l'accès à la case d'un tableau par un indice qui n'est pas connu lors de la traduction. Un premier registre contient l'adresse de début du tableau et un second registre sert au calcul de l'adresse de la case relativement au début du tableau. L'adresse de début du tableau peut aussi ne pas être connu lors de la compilation et c'est là que ce mode d'adressage prend tout son intérêt.

Support de cours Janvier 2013 39

## 4.4.3. L'adressage basé et indexé avec déplacement

Cette forme d'adressage indirect est la plus sophistiquée mais le principe est toujours le même. L'adresse offset résulte de la somme de 3 composantes : une fournie par un registre de base, une par un registre d'index et une fournie par un déplacement connu lors de la compilation.

```

// déclarations

struct {

int a, b;

} saTab[10];

int i;

// saTab[i].b = 0;

asm {

bx,offset saTab

// offset saTab : adressage immédiat

mov

si,[i]

// [i] : adressage direct

mov

// si = si+si = si*2

add

si,si

// idem, => si = 4*i

add

si,si

mov

[bx+si+2],0

// [bx+si+4] : adr. basé+indexé+déplacement

```

Dans un langage évolué, ce mode d'adressage correspondrait à l'accès à un champ d'une case d'un tableau d'enregistrements (struct du C). Le déplacement donnant, quant à lui, l'adresse du champ relativement au début de l'enregistrement. Comme précédemment, ce mode d'adressage trouve tout son intérêt lorsque l'adresse de début du tableau n'est pas connue lors de la compilation sinon on pourrait écrire "[si+saTab+2]" à la place de "[bx+si+2]". En effet, si l'adresse de saTab est connue lors de la compilation la valeur saTab+2 est calculable par le compilateur et on se retrouve avec un adressage indexé avec déplacement.

Dans le 8086, l'unité d'adressage comporte un sommateur spécialisé dans le calcul des adresses physiques. Ce sommateur fait la somme de 4 composantes : une partie segment, une partie "adresse de base" issue d'un registre de base, une partie "index" issue d'un registre d'index, une partie déplacement issue du code machine lui-même.

La partie offset résulte de la somme de 3 composantes que sont l'adresse de base, l'index et le déplacement. On peut voir l'adressage indirect, comme une version dégradée de l'adressage basé+indexé+déplacement où il l'adresse de base et l'offset valent 0. De la même façon, les autres variantes de l'adressage indirect, peuvent être vues comme une version dégradée du mode d'adressage le plus complet qu'est l'adressage basé+indexé+déplacement.

### 4.4.4. Usages des modes d'adressage

On peut résumer les usages des modes d'adressage de la façon suivante :